14<sup>th</sup> International "Hiroshima" Symposium on the Development and Application of Semiconductor Tracking Detectors (HSTD14)

November 16-21, 2025

Academia Sinica, Taipei

# **Evaluation of Radiation-Tolerant Photodiodes for CMOS Image Sensors**

Yuanfei Cheng, **Jianpeng Deng**, Changqing Feng, Pengxu Li, Tianyu Li, Xinglong Li, Difei Liu, Zhiping Luo, Ping Yang, Hongbo Zhu<sup>⊠</sup>

# **Motivation and Challenge**

# Medical Space

# **Biology**

# Particle Physics Nuclear Power Plant

**Medical CT**

**Space Station**

**Mars Rover**

Electron Microscope

Particle Collider

Thermonuclear Fusion Reactor

10rad

1krad

10krad

100krad

1Mrad

10Mrad

100Mrad

1Grad

Commercial Camera

Radiation-hardened CMOS Image Sensors are critical for applications where humans cannot safely go!

Safe to humans

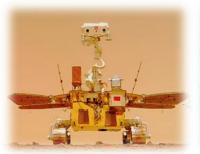

# Typical CIS architecture<sup>[1-2]</sup>

- Photon-to-Charge, Charge-to-Voltage Conversion

- Signal Readout

- ♦ Analog-to-Digital Conversion

- Data Processing and Transmission

# **Photodiode Performance Degradation**

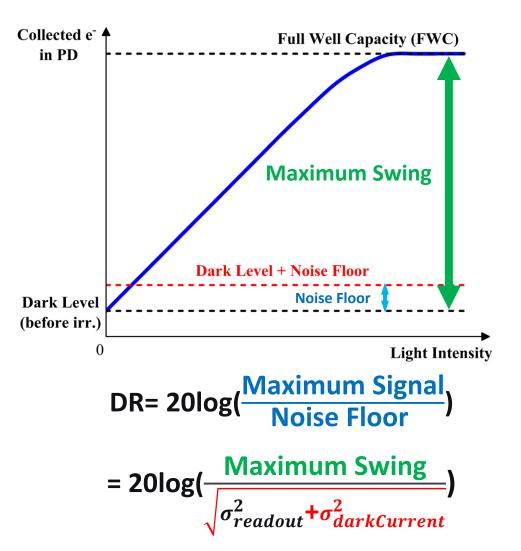

**Dynamic Range:** Ratio of the maximum to the minimum measurable light intensities

PD Degradation Caused by TID<sup>[3]</sup>

- **♦** Total Ionizing Dose

- Inducing high dark current!

- ◆ Displacement Damage Effects

- ◆ Single Event Effects

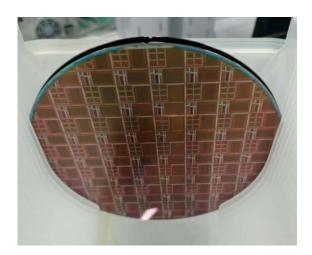

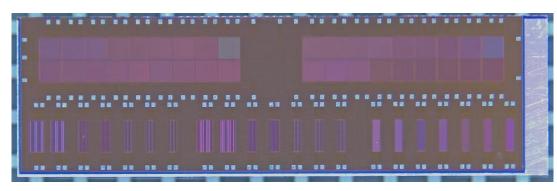

# **Overview of the Engineering Sample Chip**

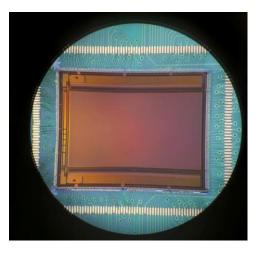

Silicon Wafer

Full-sized sensor

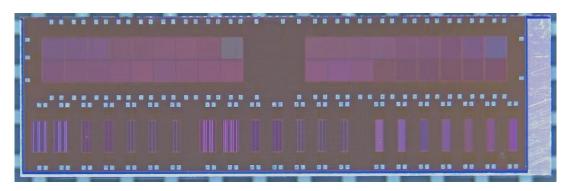

Photo of the passive arrays (2.5 mm  $\times$  8 mm)

# RadHard sensor fabricated with a 180 nm CIS process, include:

- Two 1280×720 full-sized sensor designs

See Pengxu Li's talk

- Six 256×256 test pixel arrays

- Passive photodiode arrays

Main foucs of today's talk

Several PD structures are inspired by the pioneering work<sup>[2-8]</sup> of V. Goiffon et al.

## **Passive Arrays**

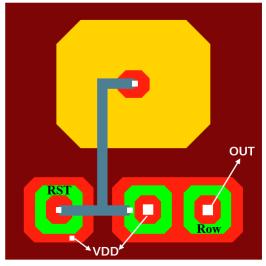

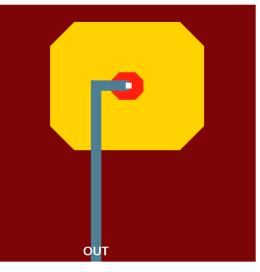

Passive pixel (10  $\mu$ m × 10  $\mu$ m)

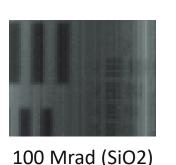

Designed dedicated passive photodiode arrays for direct assessment of the induced dark current after being exposed to different TID radiation levels

Photo of the passive arrays (2.5 mm  $\times$  8 mm)

Each individual photodiode array consisting of 1024 (32×32) pixels, they are read out in parallel

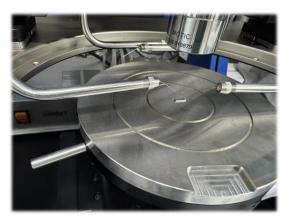

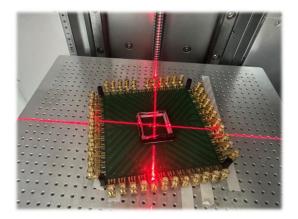

#### **Experimental Setup**

Background bias current

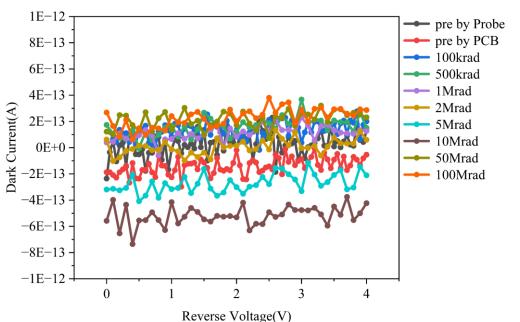

- Dark current measured with bare chips using a probe station and also with chips wire-bonded to PCB with low leakage design; consistent results obtained for chips before irradiation

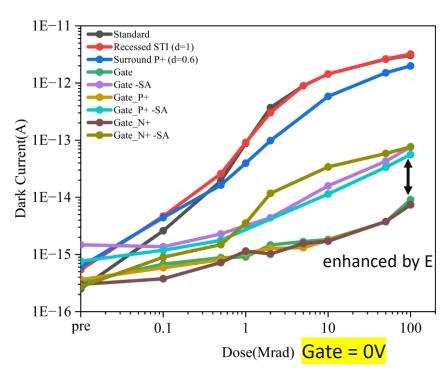

- Measurements repeated for bonded chips (powered off) after irradiation with X-ray machine up to 100 Mrad (SiO2)

- Subsequent measurements normalized by 1024 to represent the dark current of single photodiode

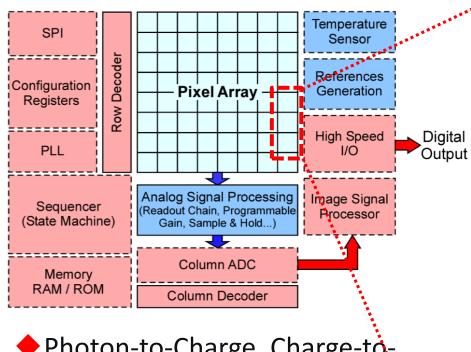

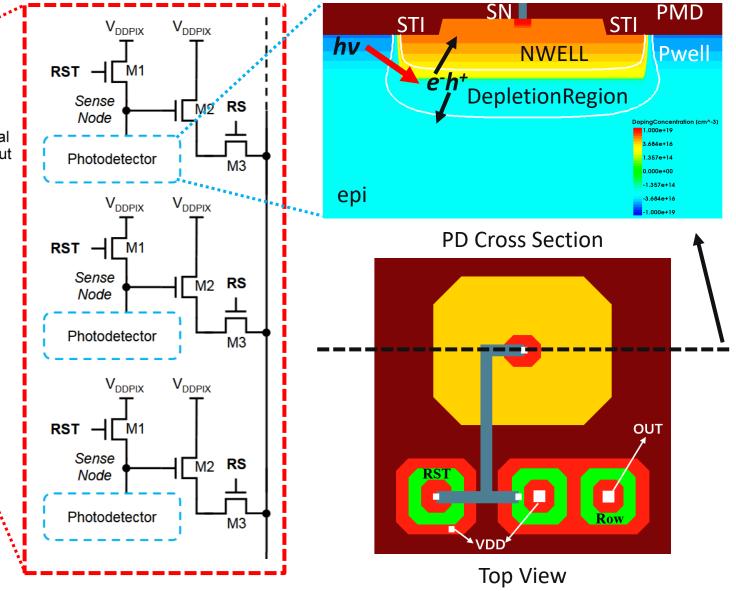

#### **Dark Current in Photodiode**

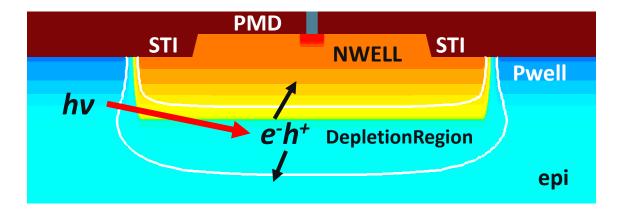

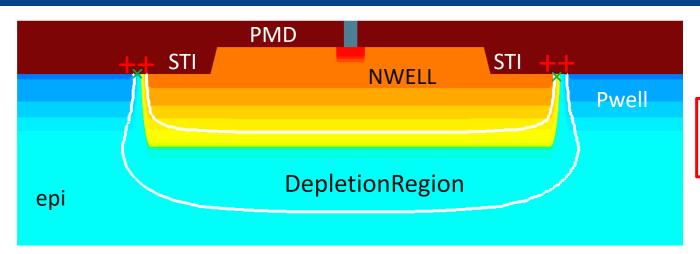

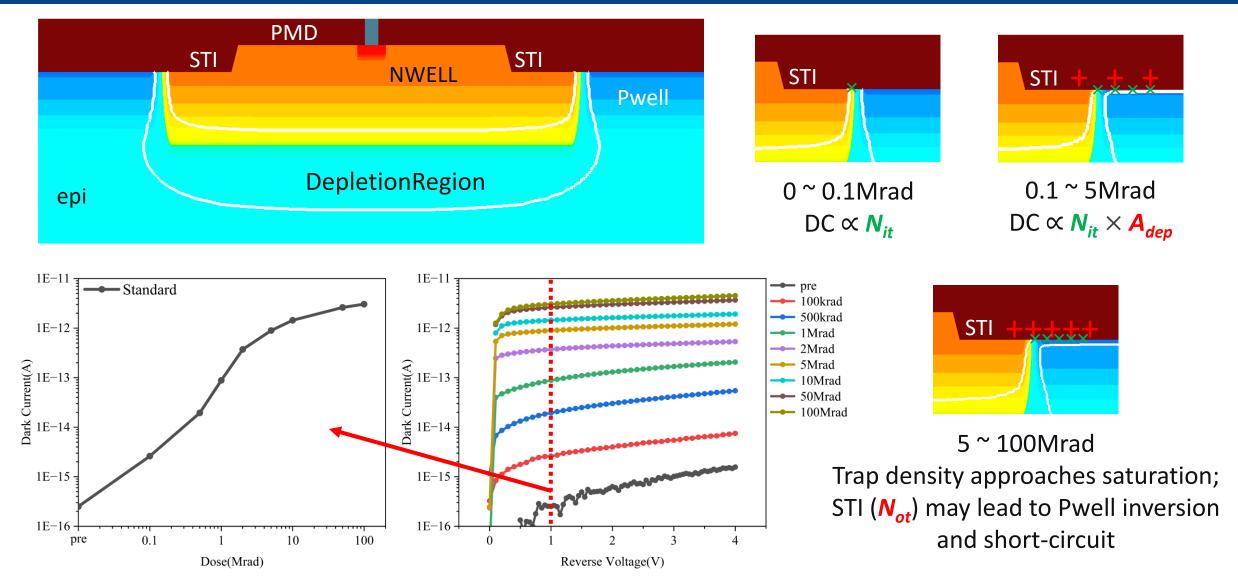

\*STI = Shallow Trench Isolation \*PMD = Pre-Metal Dielectric

+: Oxide Positive Trapped Charge(Not)

$\times$ : Interface Trap  $(N_{it})$

**Increases with TID**

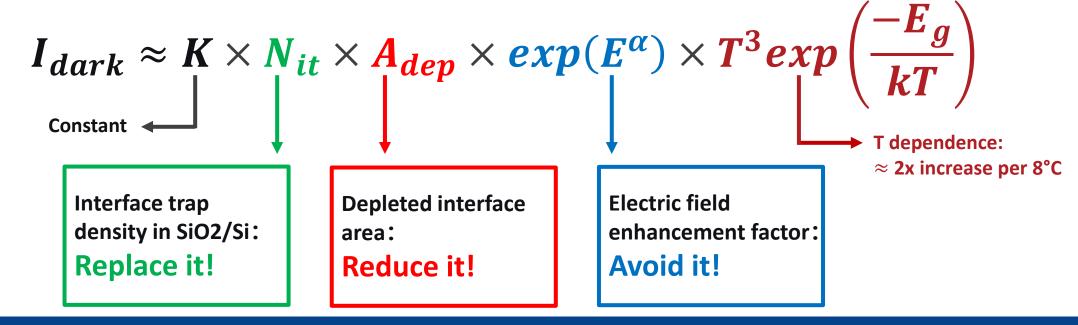

Surface as the dominant source of dark current, explainned by the **SRH mechanism**<sup>[1-2]</sup>:

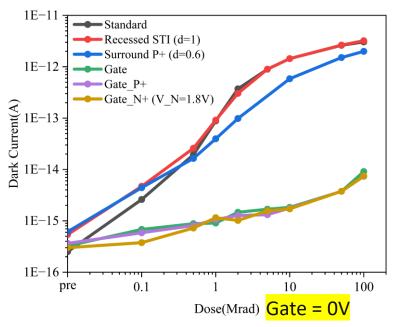

#### **Standard Photodiode**

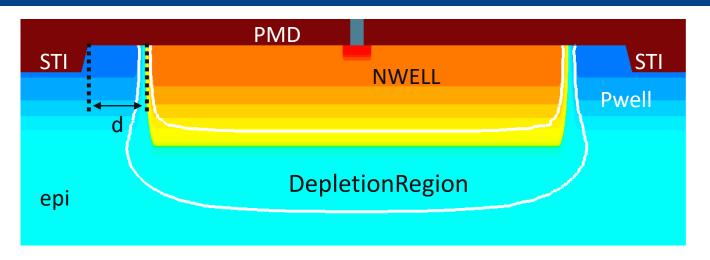

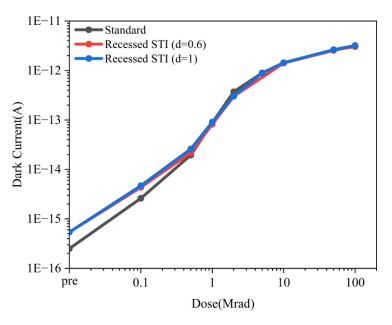

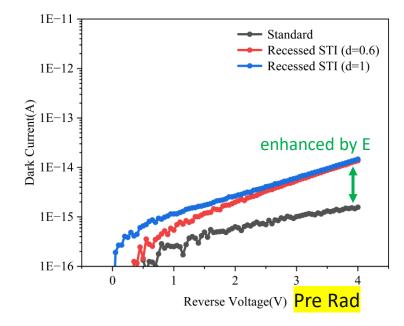

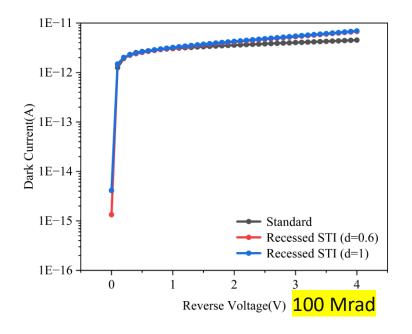

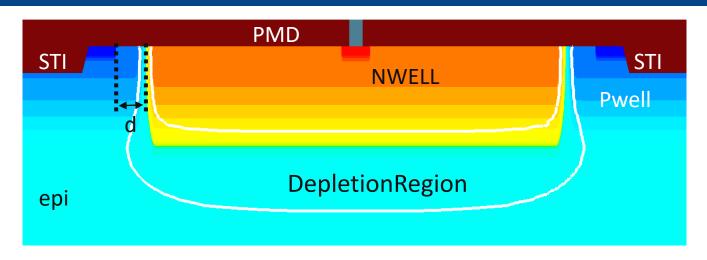

#### **Recessed STI**

- Replace the Oxide in the depleted interface from STI to PMD

- The interface of PMD as dirty as the STI

- High E-field between the Nwell and surface Pwell

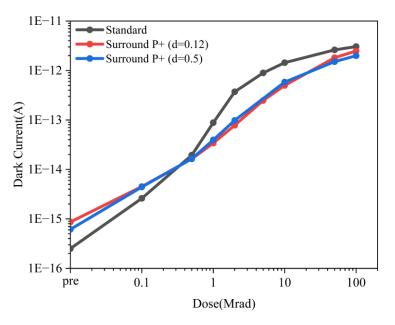

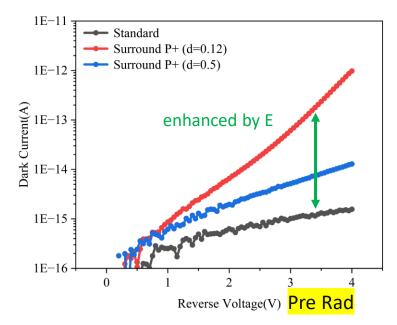

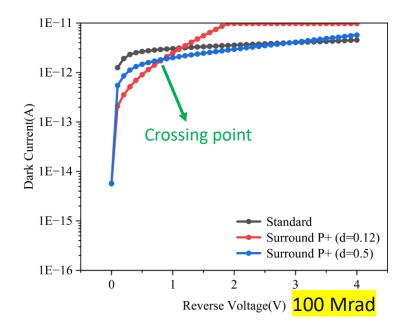

## Surrounding Nwell by a P+ Ring

- Reduce the A<sub>dep</sub> by P+ ring to prevent the depletion region from extending

- High E-field between the Nwell and surface P+

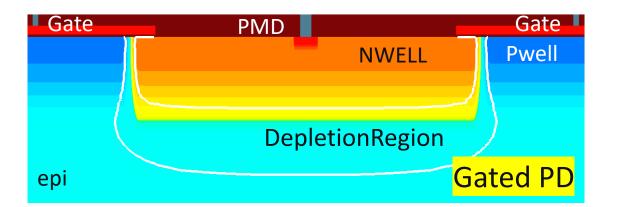

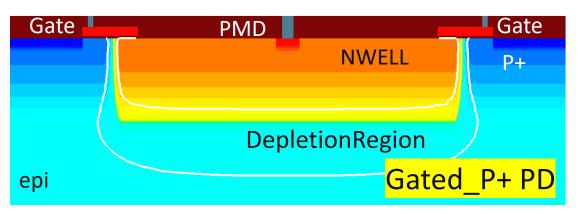

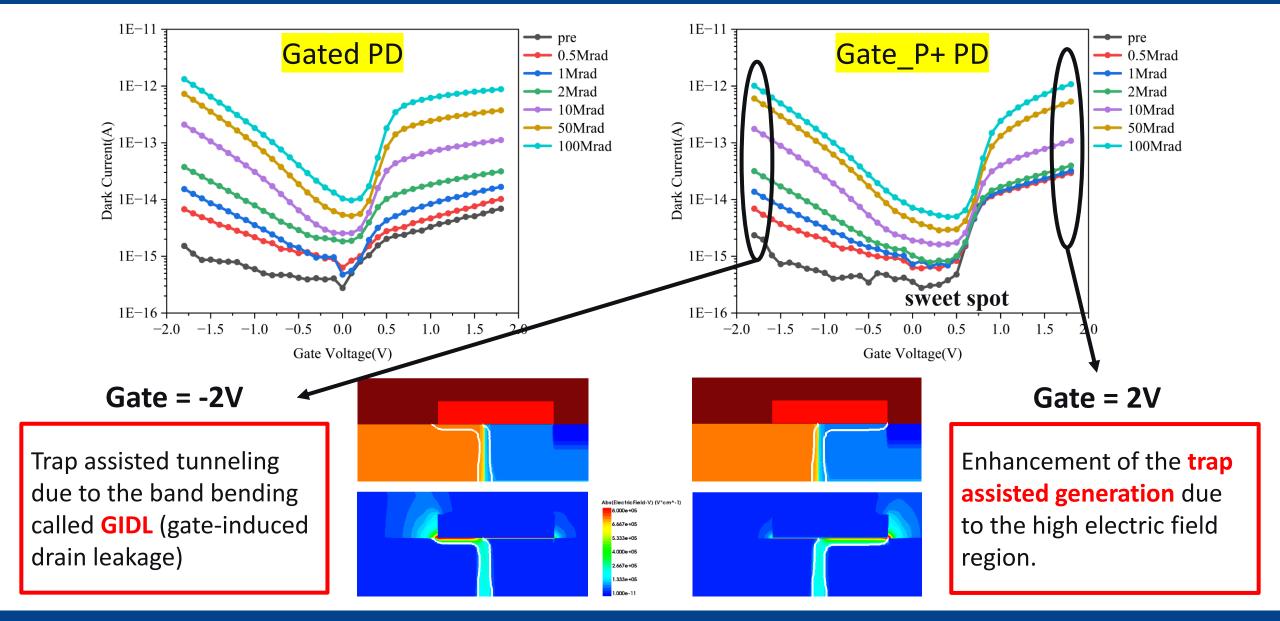

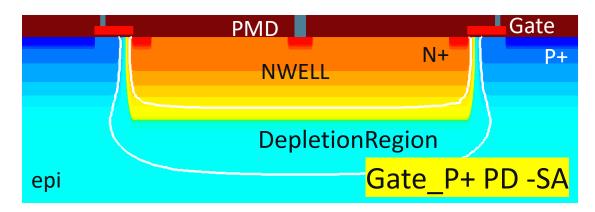

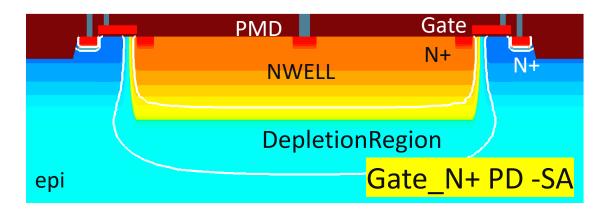

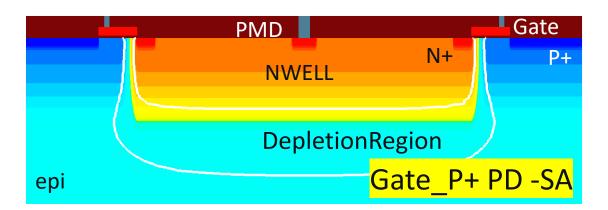

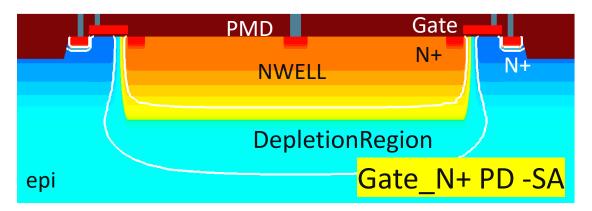

#### **Gated Photodiode**

- Gate oxide: a much high purity oxide compared with STI and PMD

- The addition of a pure gate fully covers the depleted interface area  $A_{dep}$ , resulting in a significantly reduced  $N_{it}$  and little  $N_{ot}$

A highly effective radiation-tolerant Photodiode at 100 Mrad

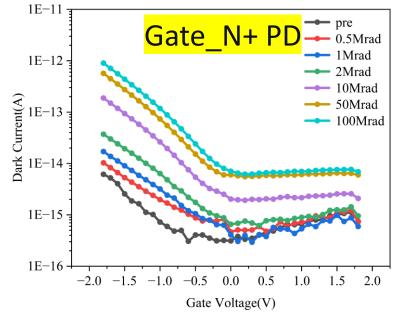

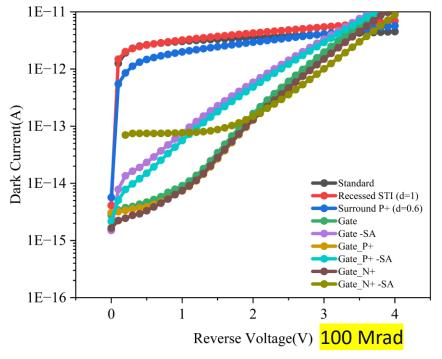

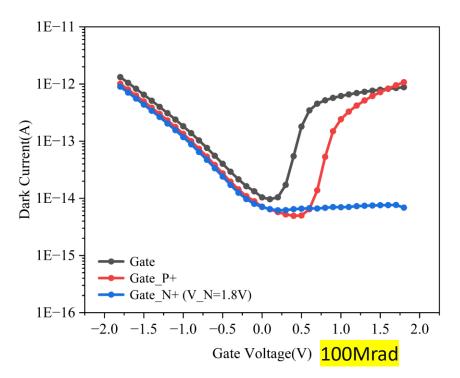

# "U-Shaped" DC-Vg Curve

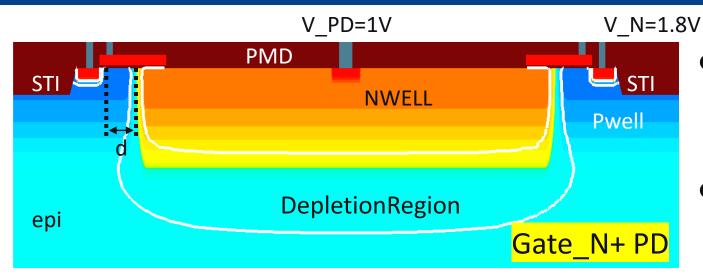

# Replacing P+ with N+

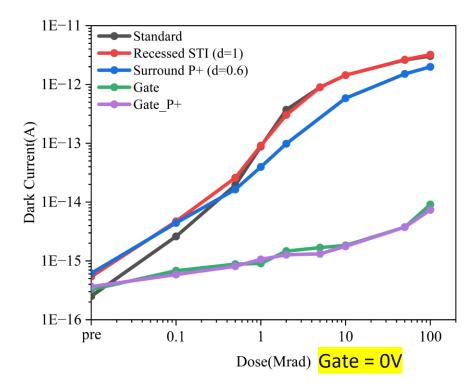

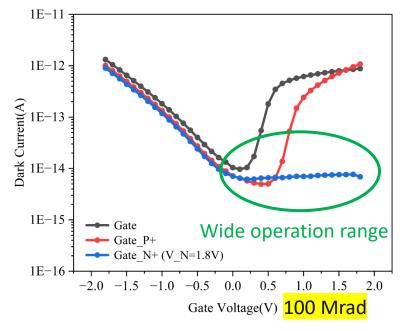

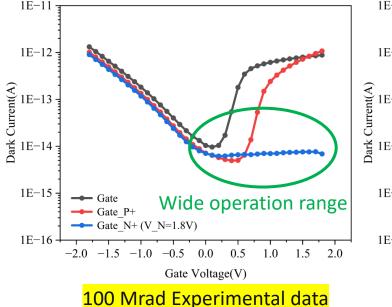

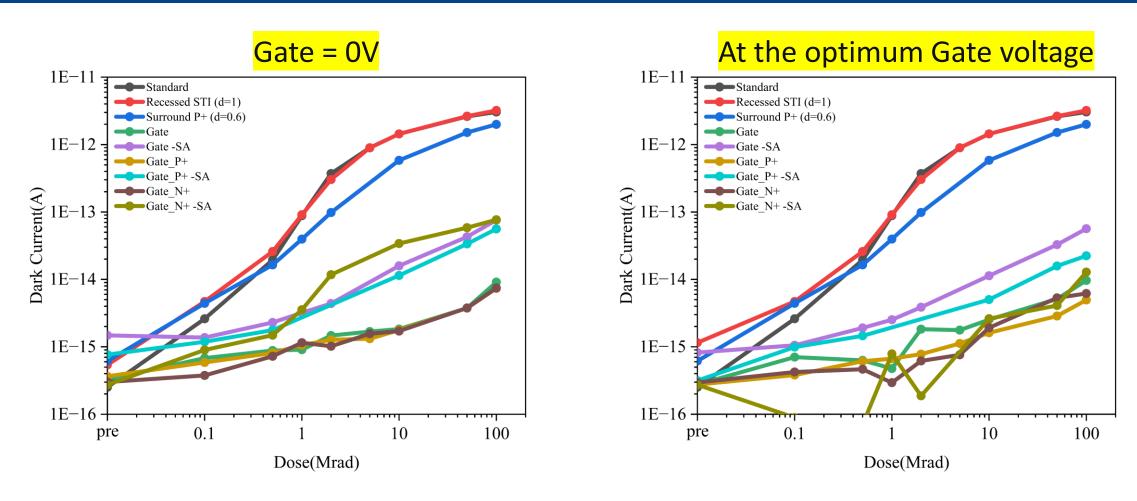

- Consistent trend across three gate structures: dark current maintaining a value around 10 fA up to 100 Mrad

- dark current of the Gate\_N+ remains stable under positive gate bias at high TID level

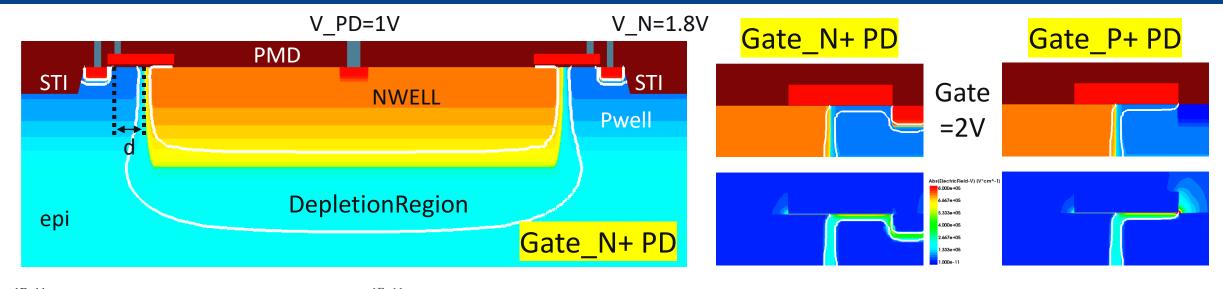

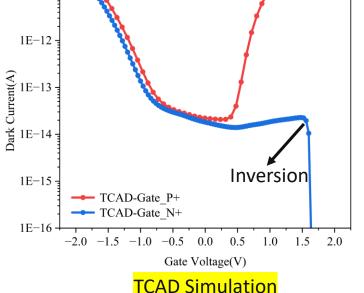

# Mitigation of High E-Field

- The Gate\_N+ PD structure capable of suppressing local high E-fields during positive gate bias

- Key optimization of "d": avoid premature P-well inversion

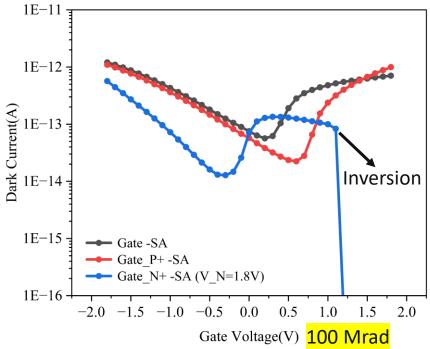

# **Manual or Self-Alignment?**

The Self-aligned structure ensures gate oxide coverage of the surface depletion region (standard process), but at the cost of an enhanced electric field

# **Manual or Self-Alignment?**

Self-Aligned Gated

PDs with still higher

dark current than

Manual Overlap at

optimal operating

voltage

# **Summary**

- Evaluation of different Radiation-Tolerant Photodiodes:

Gate > Gate-SA > Surround P+ > Recessed STI = Standard

- ➤ Gate\_N+ Photodiode demonstrates the highest radiation tolerance (~10 fA at 100 Mrad) and remains stable under positive gate bias

- Future plan:

- Perform irradiation testing up to 1 Grad (SiO2)

- Extract the oxide charge and interface state densities at different dose levels, and establish a reliable model to assisit future designs

#### References

- [1]K. D. Stefanov, CMOS Image Sensors: IOP Publishing, 2022. doi: 10.1088/978-0-7503-3235-4.

- [2]V. Goiffon, "Part III Hardening Techniques for Image Sensors," 2021 NSREC Short Course, 2021.

- [3]V. Goiffon, P. Cervantes, C. Virmontois, F. Corbiere, P. Magnan, and M. Estribeau, "Generic Radiation Hardened Photodiode Layouts for Deep Submicron CMOS Image Sensor Processes," *IEEE Transactions on Nuclear Science*, vol. 58, no. 6, pp. 3076–3084, Dec. 2011, doi: 10.1109/TNS.2011.2171502.

- [4]V. Goiffon *et al.*, "Multi-MGy Radiation Hard CMOS Image Sensor: Design, Characterization and X/Gamma Rays Total Ionizing Dose Tests," *IEEE Trans. Nucl. Sci.*, vol. 62, no. 6, pp. 2956–2964, Dec. 2015, doi: 10.1109/TNS.2015.2490479.

- [5]V. Goiffon *et al.*, "Radiation Hardening of Digital Color CMOS Camera-on-a-Chip Building Blocks for Multi-MGy Total Ionizing Dose Environments," *IEEE Transactions on Nuclear Science*, vol. 64, no. 1, pp. 45–53, Jan. 2017, doi: 10.1109/TNS.2016.2636566.

- [6]O. Marcelot, V. Goiffon, S. Rizzolo, F. Pace, and P. Magnan, "Dark Current Sharing and Cancellation Mechanisms in CMOS Image Sensors Analyzed by TCAD Simulations," *IEEE Transactions on Electron Devices*, vol. 64, no. 12, pp. 4985–4991, Dec. 2017, doi: 10.1109/TED.2017.2762433.

- [7]V. Goiffon *et al.*, "Total Ionizing Dose Effects on a Radiation-Hardened CMOS Image Sensor Demonstrator for ITER Remote Handling," *IEEE Transactions on Nuclear Science*, vol. 65, no. 1, pp. 101–110, Jan. 2018, doi: 10.1109/TNS.2017.2765481.

- [8]S. Rizzolo *et al.*, "Radiation Hardness Comparison of CMOS Image Sensor Technologies at High Total Ionizing Dose Levels," *IEEE Transactions on Nuclear Science*, vol. 66, no. 1, pp. 111–119, Jan. 2019, doi: 10.1109/TNS.2018.2884037.

# Back up

### **Comparison of Different Structures**

Gate > Gate-SA > Surround P+ > Recessed STI = Standard